本文提出了一种基于对称耦合读取谐振器(SRO)的双轨量子比特(Dual-Rail Qubit)擦除检测方案。通过实现色散位移匹配(χ-matching),研究团队在 384 ns 内达成了单发擦除检测,并首次展示了与逻辑门操作并行的连续擦除监控,逻辑门保真度达到 SOTA 水平。

TL;DR

在量子纠错(QEC)的战场上,**擦除量子比特(Erasure Qubits)正因其能将物理错误转化为已知位置的“擦除事件”而备受瞩目。近日,来自亚马逊量子计算中心(Amazon Center for Quantum Computing)的研究团队通过一种巧妙的对称耦合读取谐振器(SRO)**设计,在双轨 Transmon 平台上实现了极低扰动、高速且可并行的擦除检测。这项技术不仅简化了硬件架构,更通过“连续监控”模式为未来的软信息解码铺平了道路。

动机:为何“擦除”检测如此之难?

擦除编码的核心优势在于:如果能在错误发生时立即发出“警报”(Heralded Error),纠错码的阈值将大幅提升。然而,传统的检测方法通常需要引入复杂的辅助比特(Ancilla),这不仅增加了硬件足迹,还会因为辅助比特本身的噪声引入额外的残余错误。

在此背景下,如何利用现有的读取谐振器,在不区分逻辑态 和 (避免测量诱导退相干)的前提下,精准识别系统是否跌落至基态 (即发生擦除),成为了硬件设计的难点。

核心技术:色散位移匹配 (χ-matching)

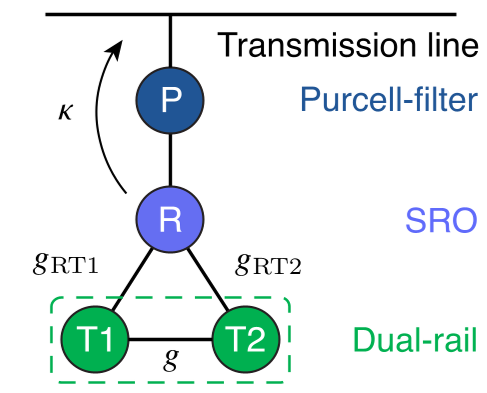

作者的核心 Insight 在于利用对称性。通过调节两个耦合 Transmon 的频率,使其在大失谐极限下与读取谐振器达成对称耦合。

图 1:(a,b) 设备原理图,两个 Transmon 对称耦合至谐振器;(c,d) 频率位移示意图,展示了逻辑空间与擦除态的色散差异。

图 1:(a,b) 设备原理图,两个 Transmon 对称耦合至谐振器;(c,d) 频率位移示意图,展示了逻辑空间与擦除态的色散差异。

在这种配置下,逻辑态 和 对谐振器产生的色散位移极其接近(即 )。这意味着当谐振器被探测时,它无法通过相位变化分辨出比特处于哪一个逻辑态,从而保护了量子相干性。而一旦发生擦除(进入 态),谐振器的频率会发生显著跳变,触发“警报”。

实验战绩:从单发检测到连续监控

研究团队在 4.5 GHz 的匹配点进行了详尽表征:

- 单发检测 (Single-shot):在 384 ns 内完成检测,分离误差仅 0.8%。通过插值随机编译(ILRB)表征,单次检查的残余误差仅为 ,这已达到了纠错算符的高性能标准。

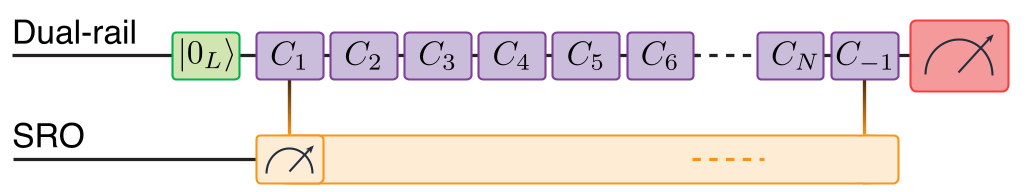

- 连续并行监控 (Continuous Monitoring):这是本研究最惊艳的部分。由于 -matching 的高性能,检测脉冲可以“一直开启”,同时进行单比特逻辑门操作。

图 2:连续监测下的随机编译结果。红色曲线展示了并行检测有效剔除擦除事件后,极高的逻辑门保真度。

图 2:连续监测下的随机编译结果。红色曲线展示了并行检测有效剔除擦除事件后,极高的逻辑门保真度。

实验结果显示,这种并行方案将 X90 门的错误率维持在 ,且检测行为本身几乎不引入额外噪声。更重要的是,连续监控提供了时间分辨率——我们可以确切知道擦除发生在门操作序列的哪一刻。

深度洞察:软信息的未来

为什么连续检测如此重要?

- 零时间开销:传统的检测需要停下逻辑操作,等待数十到数百纳秒。并行检测彻底消除了这一 Overhead。

- 软信息 (Soft Information):传统的擦除检测给出的结果是“是或否”的判决。而连续电流记录(图 5e)包含丰富的概率信息。未来的解码器(如量子 LDPC 码解码器)可以利用这些“软”概率来更智能地估算错误权重,从而进一步提升纠错极限。

总结与展望

这项工作不仅在超导硬件上实现了高性能的擦除检测,更通过去掉辅助比特,极大地提升了系统的可扩展性。虽然目前仍存在驱动诱导的穿隧效应导致擦除率略微升高,但随着 T1 寿命的提升和 TLS(双能级系统)缺陷的控制,基于对称耦合架构的双轨比特有望成为构建大规模容错量子计算机的核心基石。

本文为学术前沿解读,旨在剖析 arXiv 最新论文背后的物理直觉。更多细节请参考原论文。